- 您现在的位置:买卖IC网 > Sheet目录362799 > EVAL-AD1833EB (Analog Devices, Inc.) Multichannel 24-Bit, 192 kHz, DAC

REV. 0

–3–

AD1833A

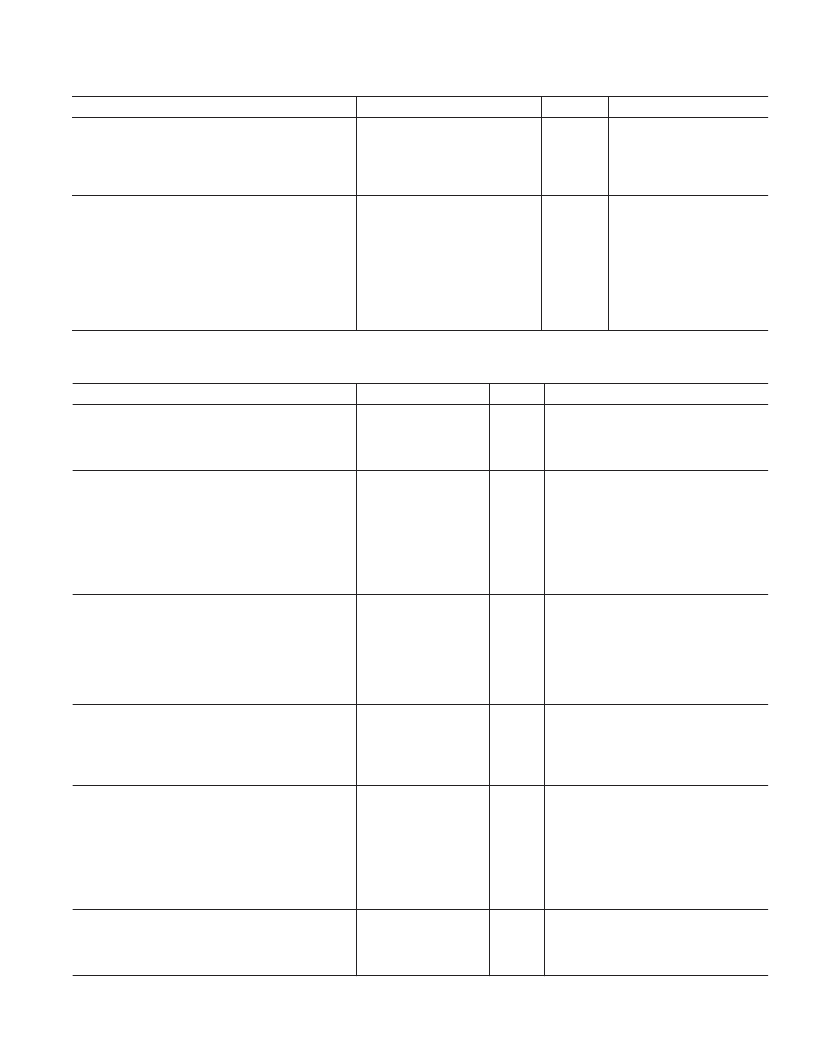

Parameter

Min

Typ

Max

Unit

Test Conditions

DIGITAL I/O

Input Voltage HI

Input Voltage LO

Output Voltage HI

Output Voltage LO

2.4

V

V

V

V

0.8

DV

DD2

– 0.4

0.4

POWER SUPPLIES

Supply Voltage (AV

DD

and DV

DD1

)

Supply Voltage (DV

DD2

)

Supply Current I

ANALOG

Supply Current I

DIGITAL

4.5

3.3

5

5.5

DV

DD1

42

48

V

V

mA

mA

mA

38.5

42

2

Active

Power-Down

Power Supply Rejection Ratio

1 kHz 300 mV p-p Signal at Analog Supply Pins

20 kHz 300 mV p-p Signal at Analog Supply Pins

–60

–50

dB

dB

Specifications subject to change without notice.

DIGITAL TIMING

Parameter

Min

Max

Unit

Comments

MASTER CLOCK AND RESET

t

ML

MCLK LO (All Modes)

*

t

MH

MCLK HI (All Modes)

*

t

PDR

PD

/

RST

LO

SPI PORT

t

CCH

CCLK HI Pulsewidth

t

CCL

CCLK LO Pulsewidth

t

CCP

CCLK Period

t

CDS

CDATA Setup Time

t

CDH

CDATA Hold Time

t

CLS

CLATCH Setup

t

CLH

CLATCH Hold

DAC SERIAL PORT

t

DBH

BCLK HI

t

DBL

BCLK LO

t

DLS

L/RCLK Setup

t

DLH

L/RCLK Hold

t

DDS

SDATA Setup

t

DDH

SDATA Hold

TDM MODE MASTER

t

TMBD

BCLKTDM Delay

t

TMFSD

FSTDM Delay

t

TMDDS

SDIN1 Setup

t

TMDDH

SDIN1 Hold

TDM MODE SLAVE

f

TSB

BCLKTDM Frequency

t

TSBCH

BCLKTDM High

t

TSBCL

BCLKTDM Low

t

TSFS

FSTDM Setup

t

TSFH

FSTDM Hold

t

TSDDS

SDIN1 Setup

t

TSDDH

SDIN1 Hold

AUXILIARY INTERFACE

t

AXLRD

L/RCLK Delay

t

AXDD

Data Delay

t

AXBD

AUXBCLK Delay

15

15

20

ns

ns

ns

24 MHz clock, clock doubler bypassed

24 MHz clock, clock doubler bypassed

20

20

80

10

10

10

10

ns

ns

ns

ns

ns

ns

ns

To CCLK rising

From CCLK rising

To CCLK rising

From CCLK rising

15

15

10

10

10

15

ns

ns

ns

ns

ns

ns

To BCLK rising

From BCLK rising

To BCLK rising

From BCLK rising

20

10

ns

ns

ns

ns

From MCLK rising

From BCLKTDM rising

To BCLKTDM falling

From BCLKTDM falling

15

15

256 f

S

20

20

10

10

15

15

ns

ns

ns

ns

ns

ns

To BCLKTDM falling

From BCLKTDM falling

To BCLKTDM falling

From BCLKTDM falling

10

10

20

ns

ns

ns

From BCLK falling

From BCLK falling

From MCLK rising

*

MCLK symmetry must be better than 60:40 or 40:60.

Specifications subject to change without notice.

(Guaranteed over –40 C to +85 C, AV

DD

= DV

DD

= 5 V

10%)

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-AD1837EB

2 ADC, 8 DAC, 96 kHz, 24-Bit Codec

EVAL-AD1837AEB

2 ADC, 8 DAC, 96 kHz, 24-Bit Codec

EVAL-AD1838AEB

2 ADC, 6 DAC, 96KHZ 24 BIT CODEC

EVAL-AD1852EB

24-Bit Stereo DAC Evaluation Board

EVAL-AD1870EB

Single-Supply 16-Bit Stereo ADC

EVAL-AD1896EB

Automotive Low-Cost Non-Volatile FPGA Family; Voltage: 1.2V; Grade: -5; Package: Lead-Free ftBGA; Pins: 256; Temperature: AUTO; LUTs (k): 8

EVAL-AD1928EBZ

2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1928EB

2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

相关代理商/技术参数

EVAL-AD1835AEB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1835EB

制造商:Analog Devices 功能描述:Evaluation Board For AD1835 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1836AEB

制造商:AD 制造商全称:Analog Devices 功能描述:Multichannel 96 kHz Codec

EVAL-AD1837AEB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1837EB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1838AEB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1838EB

制造商:Analog Devices 功能描述:Evaluation Board For 2 ADC, 8DAC 96 KHz, 24-Bit Sigma Delta Codec 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1839AEB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk